通用頻率綜合器芯片是一種以高精度參考源為基礎,生成精確穩定輸出頻率的電子設備,其工作原理通常基于鎖相環(PLL)或直接數字合成(DDS)等技術,通過集成壓控振蕩器(VCO)、鑒相器、環路濾波器等組件實現頻率的合成與調節。?

?鎖相環(PLL)是通用頻率綜合器的核心架構?,它通過反饋控制環路鎖定輸出頻率與參考頻率的相位關系。具體過程包括:鑒相器比較參考時鐘信號與分頻后的輸出信號之間的相位差,產生誤差電壓;該電壓經環路濾波器平滑后驅動壓控振蕩器(VCO),調整其輸出頻率直至相位差為零,從而實現輸出頻率的精確控制。

直接數字合成(DDS)則采用數字信號處理技術生成頻率?,其核心是一個相位累加器,對頻率控制字進行累加,輸出的相位值通過查找表轉換為數字幅度值,再經數模轉換器(DAC)和低通濾波器輸出模擬信號。DDS具有高頻率分辨率和快速轉換時間的優點,但通常需與PLL結合以提升高頻性能和抑制相位噪聲。?

工采網代理的MS5351M是一款通用頻率綜合器芯片,通過I2C配置,可產生從2.5kHz至200MHz的任意時鐘輸出。可替代晶體、晶體振蕩器、鎖相環、輸出緩沖器。

現代通用頻率綜合器芯片常采用混合架構?,如DDS+PLL,其中DDS提供高分辨率的低頻參考信號,PLL對其進行倍頻以生成高頻輸出,兼顧了頻率靈活性和頻譜純度。設計時需優化環路濾波器、電源去耦及PCB布局,以降低噪聲和提高穩定性。?

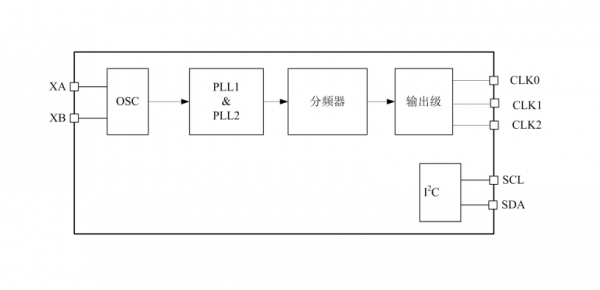

內部框圖:

時鐘發生芯片 - MS5351M的特性:

可3通道輸出從2.5kHz至200MHz時鐘

輸出頻率誤差0ppm

高分辨率、低輸出抖動

可工作在25MHz或27MHz石英晶體

輸出時鐘相位可調

輸出延時可調

輸出時鐘上升/下降時間可控

頻率切換無毛刺

相互獨立的電源供電管腳

內部核心電路電源VDD:2.5V或3.3V

輸出級電源VDDO:1.8V或2.5V或3.3V

內部高電源抑制比

兼容HCSL和PCIE Gen 1

時鐘芯片 - MS5351M的應用:

高清電視,機頂盒

打印機,掃描儀,投影儀

手持設備

網絡/通信

服務器

石英晶體/晶振/鎖相環替代

在國產時鐘發生芯片領域,瑞盟科技便是國產品牌中的佼佼者。了解更多關于瑞盟科技國產時鐘發生芯片的技術應用,聯系ISweek工采網“在線客服”獲取產品PDF、技術支持和DEMO板、可申請樣片。

轉載請注明出處:傳感器應用_儀表儀器應用_電子元器件產品 – 工采資訊 http://www.iohhome.com/43948.html